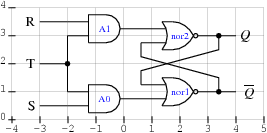

Fichier circuit_04.jps — Modifié le 3 Mai 2006 à 14 h 39

Source

uselogic

-4.5 5.5 setxrange

-4 5 setxrange

-.5 4.5 setyrange

0 4 setyrange

quadrillage

-4 0 setorigine

marks

[0 4] {ymark} apply

[0 5] {xmark} apply

20 setxunit

/logicUnit .25 def

/loadnodedict true def

/logicWireLength .75 def

(A) node %% declaration du noeud A

2 1 (NOR) ccpict %% cellule NOR en (0,1) (cc => plein centre)

(B) node %% declaration du noeud B

2 3 (NOR) ccpict

(C) node

Bin1 () (AND) clpict %% cellule AND centree a gauche de l'entree 1 de

%% B, sans le decalage propose par pict

(D) node

Ain0 () (AND) clpict

/R {Cin1 exch pop -3 exch} def %% le point d'abscisse -3 a la hauteur

%% de l'entree 1 de C

/S {Din0 exch pop -3 exch} def

/T {R S milieu} def

/Q {Bout exch pop 4 exch} def

/Qbar {Aout exch pop 4 exch} def

[S Din0] ligne

[R Cin1] ligne

[Qbar Aout] ligne

[Q Bout] ligne

/angleA -90 def

/angleB 90 def

Bin0 Aout (-*) pcdiag

Bout Ain1 (*-) pcdiag

[Cin0 Din1] ligne

[T Cin1 Din0 milieu] (-*) ligne

setTimes

(S) S cltext

(R) R cltext

(T) T cltext

setTimesItalic

(Q) Q crtext

#tex# $\overline Q$

Qbar crtexlabel

%% des labels sur les cellules

7 setfontsize

setTimes

bleu

(A1) Ccc cctext

(A0) Dcc cctext

(nor1) Acc cctext

(nor2) Bcc cctext